It is rare that a computer, especially a home computer, will live its entire life without ever undergoing either an upgrade or the addition of new devices. In most cases, of course, subject to the most elementary rules, such an operation is painless, without causing any special problems. But about every tenth (or even twentieth - it doesn’t matter) computer is brought to a non-working state: it often starts to freeze, refuses to perform any functions, or even just falls out into the so beloved by all of us blue screen of death. As a rule, the most likely cause of such problems lies in hardware conflicts (new and old) that did not share any hardware resources. Well, if your qualifications allow you to solve the problems that have arisen, or there is someone nearby who can help you, but if there is nothing like that? However, it’s not the gods, as you know, the pots are burned, let’s sit, think - you look, and break through, because everything is not so difficult, although the problem of compatibility of the most diverse equipment, since its inception in the mid-80s, is still not much did not decrease. The proposed article will help the user deal with one of the types of hardware resources required for equipment, and most often the root cause of all kinds of conflicts - with hardware interrupts (IRQ).

System hardware resources

Components can require three main types of different hardware resources to function. Almost every device uses one or more I/O ports. IN this case I don't mean a serial or parallel port, but just a special address, something like an address in RAM. These ports work special teams the central processor, with the help of which any information is either written to the port or read from it. Often, the exchange of information between the processor and the device goes only through ports, and some devices take on a dozen or even more port addresses, each of which serves to perform a specific function.

Direct Memory Access (DMA) channels are used much less frequently. This type of interaction is intended for devices that exchange large blocks of data with RAM, for example, disk drives or printers. The entire exchange bypasses the central processor, which only initiates the exchange operation and immediately proceeds to perform other work. This approach can significantly increase the performance of the entire system.

And the third type of resource is hardware interrupts, which are the basic mechanism for the system to respond to external events. Hardware interrupts, commonly called IRQs (Interrupt ReQuests), are physical signals that the device controller uses to inform the processor to process a request. Conventionally, the interrupt handling scheme may look like this:

- the processor receives the interrupt signal and its number;

- using a special table, the address of the program responsible for handling the interrupt with the given number is found - the interrupt handler;

- the processor suspends the execution of the current task, saves intermediate results and switches to the execution of the interrupt handler;

- the processor accesses the device and checks the cause of the interrupt;

- the requested actions are launched - initialization, device configuration, data exchange, etc.;

- when all necessary operations are completed, the processor returns to the interrupted task.

Unlike software interrupts triggered by an executing application program, hardware interrupts can occur at the most unexpected times, and moreover, multiple interrupts can occur at the same time. In order for the system not to "think too much" about which interrupt to service in the first place, there is a special priority scheme. Each interrupt is assigned its own unique priority. If several interrupts arrive at the same time, then the system gives preference to the highest priority, postponing the processing of other, less important, interrupts for a while.

Interrupt distribution

Consider how interrupts are usually distributed in a standard computer. Some of the numbers are strictly tied to certain devices, some can be released and used for your needs. Let's start in order:

- IRQ 0- interrupt the system timer. Generated 18.2 times per second. Used in this capacity since the creation of the first IBM PC (this number is not available for other uses);

- IRQ 1- keyboard interrupt. Generated by the keyboard controller each time a key is pressed (the number is not available for other uses);

- IRQ2 in XT-class computers, which used only 8 interrupt lines, was reserved for further system expansion and, starting with AT-class computers, was used to connect a second controller. Today IRQ 2 is used by the system for compatibility with older software, the number is not available for other uses;

- IRQ 3- interruption of the asynchronous port COM 2. The same interrupt is also used by devices operating through the COM 4 port. If desired, they can be disabled, but no one else will be able to assign IRQ 3 anyway;

- IRQ4 by analogy with the previous one, this interrupt is used by devices occupying COM 1 / COM 3 ports;

- IRQ 5 originally intended for use by the second parallel port LPT2, but then, when the second parallel port was abandoned, IRQ 5 became free. Later it was actively used by most ISA sound cards. modern PCI sound cards use this interrupt solely for compatibility with older games, the vast majority of which support SB Pro. IRQ 5 can be used for other purposes and tied to a PCI slot;

- IRQ6, starting from the first PCs, is used by the floppy controller (the number is not available for other uses);

- IRQ7- by default, interruption of the first parallel port LPT 1. If the port is disabled (if the printer is not available or is designed for USB), it can be used various devices. IRQ 7 can be tied to a PCI slot;

- IRQ8- real-time clock interrupt, first introduced in IBM AT. No other use is possible;

- IRQ 9 and IRQ 10 are free;

- IRQ 11 usually reserved for the USB bus, but can be used for other purposes (to do this, disable USB support in the BIOS);

- IRQ 12 used for a PS/2 mouse, but can be used for other purposes (if a PS/2 mouse is not available or disabled);

- IRQ 13 was originally used by the arithmetic coprocessor and is now reserved for compatibility with older software (the number is not available for other uses);

- IRQ 14 And IRQ 15 applied by the primary and secondary IDE controllers, respectively.

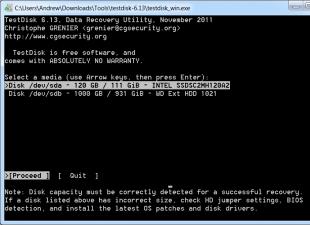

There are several ways to find out how interrupt numbers are currently distributed in your particular case. When you start the computer, even before Windows starts loading, a configuration text table appears. Immediately after it is a list of PCI devices with an indication of the IRQ number assigned to them.

Or, if you're still running Windows 9x, then there's a System icon in the Control Panel, click on it - and choose the "Devices" tab. In the properties of the "Computer" device, you can find a list of all devices with their IRQs. In Windows 2000/XP, we do not have direct access to interrupt management, so to view the list of IRQs, we need to use the standard information utility (Control Panel/Administrative Tools/Computer Management/System Information/Hardware Resources). And, finally, no one has canceled the use of utilities that test the hardware and software capabilities of a computer.

Among them, without a doubt, the most popular is SANDRA, which is able to provide the user with comprehensive information, including information about interrupts.

Device conflicts

Without going into too much detail, we can say that a conflict is a situation in which several objects simultaneously try to access the same system resource. An interrupt conflict occurs when multiple devices use the same interrupt line to send a request signal and there is no mechanism to rank these requests, causing either a failure or one of the devices to simply stop working. To clearly understand how conflicts can be avoided or eliminated, you need to understand the mechanism of IRQ management.

As you know, personal computers started with the IBM PC XT. Its architecture provided for only eight lines of hardware interrupts, which were controlled by a special controller. Each of them was assigned its own unique number, which determined the interrupt priority and the address of its handler (the so-called interrupt vector). The next version of the architecture, IBM PC AT, supplemented the existing lines with eight more, which were controlled by a second controller connected to one of the interrupt lines of the first controller. Unfortunately, this architecture stopped its development at this point, so all modern computers, despite the significantly increased number of additional devices used in them, still have only sixteen interrupt lines, one of which is reserved for emulating a second controller.

Initially, the IBM PC AT computer had only one bus, through which devices could communicate with the processor and memory - ISA. Most interrupt lines were assigned to standard ISA devices, so when the new universal PCI bus appeared, it turned out that there were only four free interrupts left on its share, denoted as INT A, INT B, INT C, INT D, so only four PCI devices can receive independent interrupts in the system. But at the same time, it must be borne in mind that the IDE controller is in a special position, which is not among those four devices only because, although it is a PCI device in terms of the data transfer method, its own interrupts IRQ 14 and IRQ are rigidly assigned to it. 15, as for older ISA devices. For the AGP bus, which is a variation of the PCI bus, INT A is "sacrificed", and the USB bus, as one of system components, connects to PCI using INT D, which reduces the number of "honest" PCI devices to only two. We should not forget about the Power Management / System Management power management subsystem, which also requires its own interruption. Thus, in real life, if there are multiple PCI devices using interrupts, it is impossible to provide them with unique hardware IRQs, and in such cases, a hardware-software method based on Plug & Play technology is used, which theoretically avoids conflicts. Although anything can happen in real life, and the remaining ISA devices still cannot share interrupt lines, therefore they are the main provocateurs of conflicts. Thus, the problem of conflict resolution is reduced to the correct distribution of interrupt numbers in case of problems with ISA devices or "buggy" drivers.

In the system, IRQ numbers are allocated twice between physical lines. The first time the system BIOS does this is when the system boots. Each Plug & Play device (and this includes all PCI, modern ISA, and all devices integrated on the motherboard) is assigned one number from among the available ones. If there are not enough numbers, several lines get one common. For PCI devices, this is not a problem - if you have normal drivers and support from the operating system, everything should work fine. But if several ISA devices or a no less "explosive" mixture of PCI and ISA devices receive the same number, then a conflict is simply inevitable, and then you will have to intervene in the process of automatic interrupt distribution. In this case, you must disable all unused ISA devices (in systems without ISA slots, they are nonetheless present: these are the COM1, COM2 ports and the drive). You can also disable the EPP and ECP modes of the LPT port, while releasing the IRQ7 interrupt. All operations for changing interrupts in BIOS Setup are carried out in the "PCI / PNP Configuration" section. There are two ways to influence IRQ number allocations: block a specific number and assign a line number directly. The first method is available for all BIOSes, the "IRQ x used by:" menu items are adjusted (in new BIOSes it is hidden in the "IRQ Resources" submenu). Those interrupts that should be assigned exclusively to ISA devices should be set to "Legacy ISA". Thus, when distributing numbers for PCI devices, these interrupts will be skipped. You should do this if any ISA device stubbornly gets on the same interrupt with the PCI device, which causes both of them to stop working. In this case, you need to find the number of this IRQ and block it. The PCI device transitions to the new IRQ number, while the ISA device stays the same. The second way to manage IRQ numbers is direct assignment, although somewhat more complicated than the first, it is much more efficient. It is very unfortunate that not all modern motherboards allow this operation. In the same BIOS Setup submenu, there may be items like "Slot X use IRQ" (other names: "PIRQx use IRQ", "PCI Slot x priority", "INT Pin x IRQ"). This option allows you to set interrupts individually for each device on the PCI and AGP bus. In this case, the following rules must be observed:

- Each PCI slot can activate up to four interrupts - INT A, INT B, INT C and INT D;

- The AGP slot can activate two interrupts - INT A and INT B;

- It is normal for each slot to be assigned as INT A. The rest of the interrupts are reserved if the PCI/AGP device requires more than one interrupt or if the requested interrupt is busy;

- AGP slot and PCI slot 1 allocate the same interrupts;

- PCI slots 4 and 5 also distribute the same interrupts;

- USB uses PIRQ_4.

Below is a table showing the relationship between PIRQ (Programmable Interrupt Request) and INT (Interrupt):

| Signal |

AGP Slot PCI Slot 1 |

PCI Slot 2 | PCI Slot 3 |

PCI slot 4 PCI Slot 5 |

| PIRQ_0 | INT A | INT D | INT C | INT B |

| PIRQ_1 | INT B | INT A | INT D | INT C |

| PIRQ_2 | INT C | INT B | INT A | INT D |

| PIRQ_3 | INT D | INT C | INT B | INT A |

Normally, you should leave the option in the AUTO position. But, if it becomes necessary to set an individual IRQ for a device on the AGP or PCI bus, first of all, it is necessary to determine in which slot the device is installed. Then, referring to the table, you can set the main PIRQ. For example, if Network Card is set to slot 3, then the main PIRQ will be PIRQ_2, because all slots are assigned to INT A, if possible. After that, the desired IRQ is selected, assigning it the appropriate PIRQ value. Just remember that the BIOS will try to assign a PIRQ to INT A for each slot. So, for AGP and PCI 1 slots, the main PIRQ is PIRQ_0, while for PCI slot 2, the main PIRQ is PIRQ_1, and so on. Second time interrupt numbers are allocated operating system, although Windows 9x begins to interfere with the actions performed by the BIOS only in extreme cases. In Windows 98, the IRQ distribution system is managed using the standard device manager. In the list of system devices, you need to find the PCI bus.

There is a special tab in its properties. If everything is set up correctly, the miniport will be mentioned there ("loaded successfully") and PCI bus steering (steering) will be enabled. Thus, Windows "98 has the means to control the distribution of interrupt numbers between physical lines. But since the BIOS most often does a good job with this, this mechanism is not involved. But sometimes it is simply necessary. When using outdated ISA devices that do not support Plug technology & Play, the BIOS may not notice it, giving the interrupt occupied by it to the PCI device - again a conflict. To resolve it, you need to reserve the necessary interrupt in the Windows Device Manager "98.

In addition to redundancy, you can directly set the interrupt number for the device. To do this, you need to find the "Resources" tab in its properties, disable automatic tuning and try to change the assigned interrupt number. Be careful, such an operation does not always work and can sometimes lead to completely unpredictable results.

But about Windows 2000 (as well as XP) - a separate conversation. If you have a fairly modern computer, then it probably supports the ACPI configuration interface. Windows 2000 in this case will generally ignore the actions of the BIOS and "hang" all PCI devices on one logical interrupt. In general, this will work fine (when there are no ISA devices), but sometimes problems can arise. To be able to change interrupt numbers, you must either change the HAL kernel or reinstall Windows 2000 with ACPI disabled in the BIOS. The kernel is replaced as follows: in the device manager, select "Computer / Computer with ACPI", after that you need to change the driver to " standard computer" and reboot. If this does not help, you will have to reinstall Windows 2000 again.

Final Tips

After installing a new operating system with all device drivers and making sure that it works without problems, it is worth writing down everything computer settings, especially if any changes have been made to the default settings. It is most reliable to write down such information on a regular piece of paper. Such information can be very useful when making any changes to the configured system, as well as help to solve problems that may arise if all the settings "move out" when installing new equipment (this sometimes happens too). And, most importantly, remember: most of the problems that arise are due to the low level of computer literacy of the computer owner. Therefore, one should always strive for self-education, then there will be fewer problems, and those that nevertheless arise will not seem insoluble.

A conflict is a situation in which several objects simultaneously try to access a resource that is intended for only one of them. An interrupt conflict occurs when multiple devices use the same interrupt line to send a request signal, and there is no mechanism to handle competing requests. If the driver, when receiving control, works with a different device that sent the request, then either a failure occurs, or one of the devices simply does not work.

The question arises: can several devices use the same interrupt line, or is it impossible in principle? After all, if the driver can determine who exactly the request came from, then it will only respond to signals from "its" device, ignoring all the others. But this must be agreed in advance in some way, otherwise conflict is inevitable.

The local PCI bus was designed with interrupt sharing in mind. Each PCI device must work correctly on the same interrupt line as other PCI devices. This is done as follows: the presence of a signal on the interrupt line is determined not by the front, i.e. change in the voltage level, but by the very fact of the presence of a certain voltage. Several devices can change the voltage in the line at once, becoming, as it were, in a queue for service.

Thus, sharing the same IRQ by multiple PCI devices is not, by definition, a conflict (Figure). However, sometimes problems do arise. First, not all PCI devices work correctly on the same interrupt line as others. Secondly, sometimes drivers have bugs that prevent them from correctly identifying the signal source, interfering with other drivers. Thirdly, not all devices work on the PCI bus; for example, ISA devices, which include, for example, COM / LPT port controllers, cannot share interrupts with others.

Rice. Win2000 Device Manager IRQ Map - IO PIC Intel 440BX Chipset

Rice. Win2000 IRQ MAP - IO APIC - Via KT266a Chipset

As a result, situations are possible when the computer often freezes, refuses to perform any functions, or even simply falls out into the so-called “blue screen of death”.

Apic (Advanced Programmable Interrupt Controller, Advanced Programmable Interrupt Controller)

As shown above, the interrupt line is a very scarce resource for a computer. However, with the development of the computer industry, the number of various external devices in the computer is constantly increasing. For example, on one motherboard there may be 5-6 PCI slots, an AGP slot, an integrated IDE controller, an integrated SCSI controller, an integrated 1/2 port network adapter, etc. And all these devices need interrupts. 16 IRQ lines gradually became insufficient.

APIC is an interrupt controller that allows you to use 24 hardware interrupts instead of 16. The limit of 16 hardware interrupts, unchanged since 1982, hindered installation in a personal computer additional devices. At the end of 2001, the first motherboards with APIC appeared.

Rice. Interrupt system in a multiprocessor environment.

The previous description referred to PICs designed for single processor systems. If the system includes two or more processors, this approach is no longer feasible and more complex PICs are required.

All modern x86 processors include a local APIC (local APIC). Each local APIC has 32-bit registers, an internal clock, a local timer, and two additional IRQ lines, LINT0 and LINT1, reserved for local APIC interrupts. All local APICs are connected to an external I/O APIC.

The I/O APIC contains a set of 24 IRQ lines, a 24-way interrupt redirection table, programmable registers, and a message block for sending and receiving messages on the APIC bus. Unlike the IRQ pins on the 8259A, the interrupt priority is not tied to a pin number.

Each entry in the interrupt redirection table can be individually programmed to display the interrupt vector and its priority, which processor will handle the interrupt, and how that processor will be selected. The information in the interrupt redirection table is used to translate each external signal into a message addressed to one or more local APICs via the APIC bus.

Static distribution

The IRQ signal is delivered by the local APIC listed in the corresponding interrupt redirection table entry. An interrupt is delivered to one particular CPU, multiple CPUs, or all CPUs.

Dynamic Allocation

The IRQ signal is delivered to the local APIC of the processor that is running the process with the lowest priority.

Each local APIC has a programmable job priority register that is used to calculate the priority of the current process. Intel expects this register to be updated by the operating system kernel on every process switch.

In addition to distributing interrupts across multi-APIC processors, the system allows the CPU to generate interprocessor interrupts. When a CPU wishes to send an interrupt to another CPU, it stores the interrupt vector and the target local APIC ID in the Interrupt Command Register (ICR) of its local APIC. The message is then sent over the APIC bus to the target local APIC, which issues the appropriate interrupt to its CPU.

Currently, many uniprocessor systems include an I/O APIC chip that can be configured in two ways:

1. As a standard 8259A PIC connected to the CPU. Local APIC is disabled and the two lines LINT0 and LINT1 are configured as INTR and NMI pins.

2. As a standard external I/O APIC. Local APIC is enabled and all external interrupts are received via I/O APIC.

- Alieva Elena Viktorovna, student

- Ufa State Aviation Technical University

- INTERRUPT CONTROLLER

- CONTROLLER

- HARDWARE INTERRUPT

- INTERRUPT

Interruption means the temporary interruption of the main process of computing to perform some planned or unplanned actions caused by the operation of the hardware or program. The interrupt mechanism is supported at the hardware level. Hardware interrupts occur as a response of the microprocessor to physical signal from some device (keyboard, system clock, keyboard, HDD etc.), these interrupts are asynchronous in time of occurrence, i.e. occur at random times. The interrupt controller is designed to process and arbitrate incoming service requests to the central processor from peripheral devices. Interrupts have a defined priority, which allows the interrupt controller to prioritize one device over another at a given time. In a modern computer, there are up to 16 external and peripheral devices that generate interrupts.

- Automation of workflow of a warehouse of a manufacturing enterprise

- Calls-technologies, features, application and efficiency

- Development of a model of the information system of the legal department for support and conclusion of enterprise contracts

Introduction

Interruption means the temporary interruption of the main process of computing to perform some planned or unplanned actions caused by the operation of the hardware or program. Those. it is a process that temporarily switches the microprocessor to the execution of another program and then returns to the interrupted program. By pressing a key on the keyboard, we initiate an immediate call to a program that recognizes the key, enters its code into the keyboard buffer, from which it is read by another program. Those. for a while, the microprocessor interrupts the execution of the current program and switches to the interrupt handler, the so-called interrupt handler. After the interrupt handler completes its work, the interrupted program will continue execution from the point where it was interrupted. The address of the interrupt handler program is calculated from the interrupt vector table.

The interrupt mechanism is supported at the hardware level. Depending on the source, interrupts are divided into:

- hardware- arise as a reaction of the microprocessor to a physical signal from some device (keyboard, system clock, keyboard, hard disk, etc.), these interrupts are asynchronous in time of occurrence, i.e. occur at random times;

- software- are called artificially with the help of the corresponding command from the program (int), are intended to perform some actions of the operating system, are synchronous;

- exceptions- are the reaction of the microprocessor to a non-standard situation that arose inside the microprocessor during the execution of some program instruction (divide by zero, interrupt on the TF flag (tracing)) .

Hardware interrupt system

The interrupt system is a combination of software and hardware that implements the interrupt mechanism.

The hardware of the interrupt system includes:

- microprocessor outputs - signals are generated on them that notify the microprocessor either that some external device “requests attention to it” (INTR), or that urgent processing of some event or catastrophic error (NMI) is required

- INTR - pin for input interrupt request signal,

- NMI - NMI input pin

- INTA - output for the output signal confirming the receipt of an interrupt signal by the microprocessor (this signal is fed to the input of the 8259A controller chip of the same name;

- programmable interrupt controller 8259A (designed to capture interrupt signals from eight different external devices; it is made in the form of a microcircuit; usually two serially connected microcircuits are used, so the number of possible sources of external interrupts is up to 15 plus one non-maskable interrupt; it is he who generates the number of the interrupt vector and issues its data bus);

- external devices (timer, keyboard, magnetic disks, etc.)

Interrupt handling

An interrupt triggers a series of events that occur in both hardware and software. On fig. 1 shows a typical sequence of these events.

After the I/O device terminates, the following occurs:

- The device sends an interrupt signal to the processor.

- Before responding to an interrupt, the processor must complete the execution of the current instruction (see Figure 1).

- The processor checks for an interrupt, detects it, and sends the device that sent the interrupt a signal that it received it successfully. This signal allows the device to remove its interrupt signal.

Now the processor needs to prepare to transfer control to the interrupt handler. First you need to save all important information so that you can later return to the point in the current program where it was paused. The minimum required information is the program status word and the address of the next instruction to be executed, which is in the program counter. This data is pushed onto the system control stack.

Figure 2. Handling a simple interrupt

Figure 2. Handling a simple interrupt Next, the program counter of the processor is loaded with the input address of the interrupt handler program, which is responsible for processing this interrupt. Depending on the architecture of the computer and the device of the operating system, there may be either one program for handling all interrupts, or there may be a separate handler for each device and each type of interrupt. If there are several programs to handle interrupts, then the processor must determine which one to call. This information may be contained in the initial interrupt signal; otherwise, to obtain the necessary information, the processor must poll all devices in turn to determine which one sent the interrupt.

As soon as a new value is loaded into the program counter, the processor proceeds to the next instruction cycle, proceeding to retrieve it from memory. Since the instruction is fetched from the location whose number is given by the contents of the program counter, control passes to the interrupt routine. The execution of this program entails the following operations.

The contents of the program counter and the status word of the interrupted program are already stored on the system stack. However, this is not all the information related to the state of the executable program. For example, you need to save the contents of the processor registers, since these registers may be needed by the interrupt handler. Therefore, it is necessary to save all information about the state of the program. Typically, an interrupt handler starts by pushing the contents of all registers onto the stack. Other information that should be stored is discussed in Chapter 3, Process Description and Control. On fig. a simple example is shown in which the user program is interrupted after executing an instruction from location N. The contents of all registers, as well as the address of the next instruction (N + 1), totaling M words, are pushed onto the stack. The stack pointer is updated to point to the new top of the stack. The program counter is also updated, indicating the beginning of the interrupt service routine.

Now the interrupt handler can start its work. The process of handling an interrupt includes checking status information related to the I/O operations or other events that caused the interrupt. This may also include sending additional instructions or notification messages to I/O devices.

After the interrupt processing is completed, the previously saved values are retrieved from the stack, which are again entered into the registers, thus resuming the state in which they were before the interrupt.

The last step is to restore the program status word and the contents of the program counter from the stack. As a result, the next command of the interrupted program will be executed.

Because the interrupt is not a subroutine called from the program, it is important for complete recovery to retain all state information of the interrupted program. However, an interrupt can occur at any time and anywhere in the user program. This event is unpredictable.

Interrupt controller

The interrupt controller is designed to process and arbitrate incoming service requests to the central processor from peripheral devices. By analogy, the functions of the interrupt controller can be compared with the secretary of some boss. The secretary must decide which of the visitors to admit to the boss in the first place, and which and then, based on the priorities given by the boss and the status of the visitor himself. So in a computer system, it is possible that several peripherals have sent an interrupt signal or an interrupt request. In computer literature, this signal is referred to as IRQ (Interrupt Request).

As mentioned above, interrupts have a certain priority, which allows interrupt controllers to give preference to one device at a given time, and not to another. In a modern computer, there are up to 16 external and peripherals that generate interrupts. Here are the devices:

–IRQ 0, system timer; –IRQ 1, keyboard; –IRQ 2, used to query cascaded devices; –IRQ 8, real time clock; –IRQ 9, reserved; –IRQ 10, reserved; –IRQ 11, reserved; –IRQ 12, ps/2 – mouse; –IRQ 13, coprocessor; –IRQ 14, hard disk controller; –IRQ 15, reserved; –IRQ 3, ports COM2, COM4; –IRQ 4, ports COM1,COM3; –IRQ 5, LPT2 port; –IRQ 6, drive controller; –IRQ 7, LPT1 port, printer.

Here the signals are listed in descending order of priority. You may notice that after IRQ 2, IRQ 8 follows. The fact is that at one time the interrupt controller consisted of two microcircuits, one was connected to the other. This second microcircuit is connected to the IRQ 2 line, forming a cascade. It serves the lines IRQ8-IRQ 15. And then the lines of the first microcircuit follow.

Operation of the interrupt controller

Interrupt controller operation is considered based on Intel 8259A chips, which were used in now very old computers with processors up to the 386 series. These computers usually had 2 8259A chips connected in cascade, that is, one to the other. One of the microcircuits connected via the interrupt request line directly to the processor is the master or master. The rest, connected to the master through similar conclusions, are called slaves.

Figure 3. Connection diagram of interrupt controllers and their interaction with the central processor

Figure 3. Connection diagram of interrupt controllers and their interaction with the central processor Figure 3 shows the connection diagram of interrupt controllers and their interaction with the central processor. Interrupt signals from peripheral devices or slave controllers are fed to the inputs IR0–IR7 of the master controller. The internal logic of the master controller processes incoming requests in terms of priority. If the priority of the device request is sufficient, then a signal is generated at the INT output of the controller, which is fed to the INTR input of the processor. Otherwise, the request is blocked.

If the processor enables interrupts, then after the execution of the current instruction is completed, it generates a sequence of signals on the INTA line, which puts the slave controller into a state of immunity to incoming new interrupt requests, and in addition, information from the internal registers of the controller is output to the data line, by which the processor recognizes the interrupt type.

The processor gives the interrupt permission to the interrupt controller via the bus controller. The RD signal is intended to ensure that the interrupt controller places the contents of internal registers on the data bus. On the WR signal, the interrupt controller, on the contrary, receives data from the bus of the same name and writes them to internal registers. Accordingly, this affects the mode of operation of the interrupt controller.

The CS input is connected to the address bus and this signal identifies a specific interrupt controller. Input A0 points to the interrupt controller port in the I/O space.

Inputs IR0–IR7 are designed to receive interrupt requests from peripherals and slave controllers.

The CAS0-CAS2 outputs are designed to identify a specific slave controller.

The article discusses hardware interrupts and device, functions, operation of the interrupt controller. This interrupt controller appeared in the first PC-compatible computers. Since then, both processors and the computer itself have changed in many ways, although some points remain. Therefore, in order to make it clearer, the organization of the 8295A interrupt controller was considered.

The above diagram shows the signals coming not only to the slave and master interrupt controllers, but also to the rest of the slaves. However, your computer or laptop actually has 2 interrupt controllers, as stated above: a master and a slave. But you can create your own computer systems using up to 64 slave interrupt controllers in this way.

IN modern computers a long time ago interrupt controller functions do not perform 8259A chips, but south bridge. However, for all programs and devices, everything remains the same. Moreover, the interrupt controller is programmable, and the internal registers and ports must be accessed in the same way as the 8259A controller.

Conclusion

In this paper, interrupts were considered, namely the hardware of interrupt processing and the principle of interrupt processing. Interrupt controllers and the principle of their operation are also considered.

Interruption means the temporary interruption of the main process of computing to perform some planned or unplanned actions caused by the operation of the hardware or program. The interrupt mechanism is supported at the hardware level. Hardware interrupts occur as a reaction of the microprocessor to a physical signal from some device (keyboard, system clock, keyboard, hard disk, etc.), these interrupts are asynchronous in time of occurrence, i.e. occur at random times.

Interrupt controller is designed to process and arbitrate incoming service requests to the central processor from peripheral devices. Interrupts have a certain priority, which allows interrupt controller give preference at a given time to one device over another. In a modern computer, there are up to 16 external and peripheral devices that generate interrupts.

Bibliography

- Lecture. Interrupts. Email Resource. http://hromatron.narod.ru/_lekcii/prerivania_lekcia_g2013.htm

- System interrupts | Hardware interrupt | Interrupt handling http://life-prog.ru/view_os.php?id=16

- Interrupt controller. Email Resource http://sdelaycomputersam.ru/Controller_irq.php,

- Interrupts. Interrupt controller. Device, functions, work. Email Resource http://sdelaycomputersam.ru/Controller_irq.php

- Structure and initialization of the Intel 8259A interrupt controller

I think many inquisitive users have probably come across such an abbreviation as IRQ more than once. It can be found, for example, if you like to look into the Device Manager program in Windows. If you select any device, for example, a keyboard, select the "Properties" menu item with the right mouse button, and in the window that appears, make the "Resources" tab active, then in the list of resources you will see the inscription IRQ 01.

What is IRQ and what is it for?

The abbreviation IRQ stands for Interrupt ReQuest (interrupt request). In order to understand why it is needed, one should recall the details of the organization of the work of a personal computer.

The circulatory system of a computer, through which information is exchanged between the processor and other devices, is system bus. But in general, how is the processor able to distinguish information processing requests coming over the bus from various devices?

For this, there is a system of hardware interrupts (IRQ). Each interrupt has a specific number (numbering starts from 0) and is assigned to a specific device. So, interrupt number 1 is assigned to the keyboard, hence the designation IRQ 01.

When a request is received from the device, the computer interrupts (hence the term “interruption” itself) the processing of current information and begins processing the newly received one. If there are several interrupts, then they are processed in the order of priorities assigned to each of them. As a rule, the smaller the interrupt number, the greater the priority for the processor has the device assigned to this interrupt, but this rule is not always observed.

Serves the processing of IRQ a special chip, which is called the interrupt controller. As a rule, this microcircuit is part of the central processing unit, and sometimes it is allocated as a separate chip on the motherboard. To handle each interrupt in the BIOS, there is a special firmware called an interrupt handler. The addresses of all handlers are stored in the so-called interrupt vector table.

Previously, in the first computers of the XT family, 8-bit was common, so a total of 8 interrupts were available to devices. With the advent of the 16-bit ISA bus, their number increased to 16.

Setting Interrupt ReQuest

I must say that the interrupts assigned to some devices are not fixed and can be changed programmatically. For example, IRQ is commonly used by serial Com port 2 can also use a modem installed in the expansion slot. In modern computers and operating systems that support the PnP standard and run under Windows, IRQ values for devices connected to bus slots are selected automatically.

But things weren't so simple in the old days, when the user had to manually set the IRQ value in many DOS programs. For example, when installing sound card, the user had to choose a free interrupt from a very small number of available ones (usually it was IRQ 5) and specify this value in the program being launched, for example, in some game.

In many BIOSes, it is possible to change the default IRQ values in the Setup program. This option is usually located in the IRQ Resources or PCI/PNP Configuration sections.

Setting an IRQ value for a device equal to the IRQ value already occupied by some device in most cases leads to the inoperability of one of these devices or both at once, and sometimes it is fraught with a computer freeze.

In the more modern PCI bus, the interrupt control system has been radically changed, and the interrupt control capabilities have been expanded. Thanks to IRQ Sharing technology, it has also become possible to place several devices on one interrupt channel, and external devices connected to PCI slots have the ability to automatically distribute resources among themselves.

In addition, modern computers commonly use an advanced programmable interrupt controller (APIC) that supports 24 channels of Interrupt ReQuest. The advanced interrupt controller is made in the form of two microcircuits, one of which is located in the processor itself, and the other on the motherboard. This interrupt controller first appeared in systems based on Pentium processors. However, support for the old interrupt system was retained for compatibility reasons. The next step in the development of the principles of interrupt handling is the Message Signaled Interrupts technology, support for which appeared in the Windows OS line starting with Windows Vista.

Do not confuse hardware IRQs with BIOS software interrupts, which will be discussed in a separate article. BIOS software interrupts are usually used to organize work software with I / O devices and are denoted by the abbreviation INT. Many of them are similar in function to hardware IRQs, but have different numbers.

List of Interrupt ReQuest numbers in the standard scheme for the 16-bit ISA bus:

- System timer

- Keyboard

- Optional interrupt controller (for 8-bit bus compatibility)

- Com 1 and 3 ports

- Com 2 and 4 ports

- Free (in 8-bit bus - hard disk controller)

- Controller floppy disks(FDD)

- Parallel port LPT

- CMOS real time clock

- Combined with IRQ 2

- Free

- Free

- PS/2 mouse port

- Coprocessor (currently hardly used)

- First IDE Controller

- Second IDE Controller

List of additional IRQs that the APIC Extended Interrupt Controller uses:

- USB controller

- Integrated audio subsystem (AC'97 or HDA)

- USB controller

- USB controller

- Integrated network card

- Free

- Free

- USB 2.0 controller

Correspondence of IRQ numbers and BIOS interrupts:

Table of correlation between hardware IRQ and software INT BIOS

Conclusion

So, in this article, you were able to find out what the abbreviation IRQ means and what hardware interrupts are. They are a built-in mechanism for allocating computer resources and are designed to organize device access to the central processor. Proper IRQ allocation and tuning avoids conflicts between devices and ensures stable work systems.

IRQ priority management

Hardware interrupt request management

Most of the components directly attached to the motherboard, including PCI slots, IDE controllers, serial ports, keyboard port, even the motherboard CMOS, are assigned separate IRQs. A hardware interrupt request, or IRQ, interrupts the normal operation of the processor, allowing the device to function. Windows 7 allows you to prioritize one or more IRQs (which are mapped to one or more devices), potentially improving the performance of those devices.

Steps to Change IRQ Priority

- Start by running the System Information Utility (msinfo32.exe) and open the System Information branch Hardware Resources Interrupts (IRQs) to see which IRQs are used for which devices.

- Then open the Registry Editor (see Chapter 3) and navigate to the HKEY_LOCAL_ MACHINE\SYSTEM\CurrentControlSet\Control\PriorityControl branch.

- Create a new DWORD value in this section and name the parameter IRQ#Priority, where # is the number of the IRQ device for which you want to set the priority (for example, IRQ13Priority corresponds to IRQ 13, which is an arithmetic coprocessor).

- Double click on the new value and enter the priority number. Enter 1 for the highest priority, 2 for the second, and so on. Make sure you don't enter the same number for two entries, and don't try to do it all at once, rather experiment with one or two values.

- When finished, close Registry Editor and restart your computer.

uptostart.ru News. Games. Instructions. Internet. Office.

uptostart.ru News. Games. Instructions. Internet. Office.